# mipialliance

MIPI SPMI System Power Management Interface

v1.00.00 Adopted: 4Q 2008 v2.0 Adopted: Q3 2012

## **Legal Disclaimer**

The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled by any of the authors or developers of this material or MIPI<sup>®</sup>. The material contained herein is provided on an "AS IS" basis and to the maximum extent permitted by applicable law, this material is provided AS IS AND WITH ALL FAULTS, and the authors and developers of this material and MIPI hereby disclaim all other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of negligence. ALSO, THERE IS NO WARRANTY OR CONDITION OF TITLE, QUIET ENJOYMENT, QUIET POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD TO THIS MATERIAL.

All materials contained herein are protected by copyright laws, and may not be reproduced, republished, distributed, transmitted, displayed, broadcast or otherwise exploited in any manner without the express prior written permission of MIPI Alliance. MIPI, MIPI Alliance and the dotted rainbow arch and all related trademarks, tradenames, and other intellectual property are the exclusive property of MIPI Alliance and cannot be used without its express prior written permission.

IN NO EVENT WILL ANY AUTHOR OR DEVELOPER OF THIS MATERIAL OR MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL, CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR ANY OTHER AGREEMENT RELATING TO THIS MATERIAL, WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

# **Specification SPMI**

## **Current Version**

System Power Management Interface v2.0

### **Primary Use Cases**

- Power Management Control Bus

- Dedicated commands for Reset, Sleep, Shutdown, Wakeup, Authenticate

- Low latency Register 0 Write command

- General Purpose Multi-master, Multi-slave Read/Write Bus

- · Master-to-Slave, Slave-to-Master, Master-to-Master and Slave-to-Slave Read/Write Commands

- Burst Read/Write Commands

# **Specification SPMI**

## **Major Features**

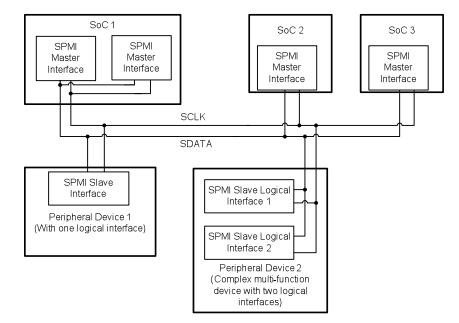

- 2-wire, bi-directional interface (SDATA, SCLK)

- Multi-Master, Multi-Slave

- Up to 4 Masters

- Up to 16 Slaves

- Request Capable Slaves

- · Able to request arbitration on the bus and send commands

- 2 Speed classifications SCLK only provided during a transaction

- Low Speed: 32kHz to 15MHz

- High Speed: 32kHz to 26MHz

- Master and Slave Arbitration for bus contention resolution

- Primary and Secondary arbitration priorities for both Masters and Slaves

- Round Robin priority algorithm for equal access to bus by Masters

- A-bit and SR-bit arbitration for Slaves

- Slave Group IDs for simultaneous write commands to multiple slaves

- 8-bit or 16-bit address access

- Burst Reads/Writes

- Up to 16 Bytes with 8-bit addressing

- Up to 8 Bytes with 16-bit addressing

- Parity bit for error detection (odd parity)

- ACK/NACK on certain commands (SPMI v2.0)

## **Specification SPMI**

#### **Advantages of SPMI**

- Replaces point-to-point topology with bus architecture to reduce interfaces and pin counts of SoCs.

- Multi-Master/Slave feature enables Chipset partitioning flexibility for complex and distributed systems.

- Distributed PMICs (Slaves) for point of load placement

- Single PMIC (Slave) for reduced part count

- Request Capable Slave messaging reduces side-band signals and pins between Slaves and Masters

- AČK/NACK to confirm correct completion of commands (SPMI v2.0)

#### **Backwards Compatibility**

- SPMI v2.0 devices are not compatible with SPMI v1.0 Master and Request Capable Slave (RCS) devices.

- SPMI v2.0 Master devices are compatible with SPMI v1.0 Non-Request Capable Slave (NRCS) devices, if the Master ignores the value present on SDATA during the ACK/NACK cycle.

#### **System Level Integration**

- Logical Masters and Slaves may be integrated onto single or multiple physical devices

- Pull down resistor may be integrated into a physical device or on the PCB

- 1.2V and 1.8V signaling voltages defined

- Up to 50pF loading on SDATA and SCLK